ว่าด้วยเจ้า Bulldozer ก่อน

เจ้ารถไถตัวนี้เป็นสถาปัตยกรรมล่าสุดของทาง AMD ซึ่งกลุ่มเป้าหมายก็คือ ตลาด Server / Worstation / Hi-End User

Specsification มีดังนี้

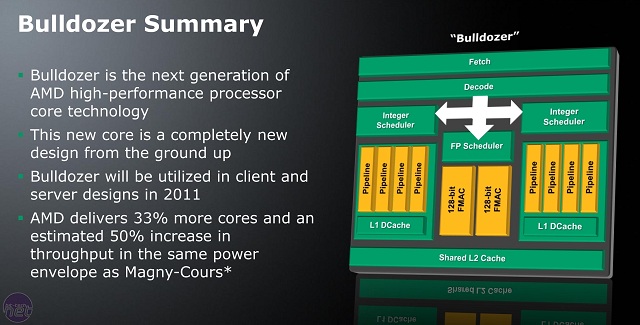

Microarchitecture

Based on the information provided by AMD during its annual Analyst Day last November, the first Bulldozer chip code-named Zambezi (which belongs to Orochi family, according to the firm) will feature eight x86 processing engines, two 128-bit FMAC floating point units, shared L2 cache, shared L3 cache as well as an Advanced Dual-Channel Memory Sub-System (IMC - Integrated Memory Controller), higher memory level parallelism that's far superior to what todays Phenom II houses. AMD also states that the new CPU will feature Extensive New Power Management Innovations. The new chips that belong to Bulldozers family will also support Advanced Vector Extensions (AVX) that supports 256-bit FP operations.

[edit] Bulldozer Design Breakdown

Two tightly coupled, "conventional" x86 out-of-order processing engines which AMD internally named module

(Single-Module ==> Dual-Core, Dual-Module ==> Quad-Core, Quad-Module ==> Octa-Core etc...)

Between 8MB to 16MB of L3 cache shared among all Modules on the same silicon die

DDR3-1866 and Higher Memory Level Parallelism

Dual channel DDR3 integrated memory controler

(support for PC3-12800 (DDR3-1600)) for Desktop,

Quad Channel DDR3 intergrated memory controller (support for PC-12800 (DDR3-1600) and Registered DDR3) for Server/Workstation (Opteron)

Cluster Multi-threading (CMT) Technology

Bulldozer module consists of the following:

up to 2048kB L2 cache inside each module

(shared between the cores in a module)

16kB 4-way L1 data cache (way-predicted) per core and 2-way 64kB L1 instruction cache per module L1 cache, Fruehe for THW

Two dedicated integer cores

- each consist of 2 ALU and 2 AGU which are capable for total of 4 independent arithmetic or memory operations per clock per core

- duplicating integer schedulers and execution pipelines offers dedicated hardware to each of two threads which significantly increase performance in multithreaded integer applications

- second integer core increases Bulldozer module die by around 12%, which at chip level adds about 5% of total die space[9]

Two symmetrical 128-bit FMAC (fused multiply-add (FMA) capability)

Floating Point Pipelines per module that can be unified into one large 256-bit wide unit if one of integer cores dispatch AVX instruction and two symmetrical x87/MMX/3DNow! capable FPPs for backward compatibility with SSE2 non-optimized software

32nm SOI process with implemented first generation GF's High-K Metal Gate (HKMG)

Support for AMD's only SSE5 128-bit instructions

- incl. three smaller supplemental extensions CVT16, XOP and FMA4 instruction set, which are now part of SSE5 specification (since May 2009 revision)

Support for Intel's Advanced Vector Extensions (AVX) (Supports 256-Bit FP Operations via AVX)SSE4.1, SSE4.2, AES, CLMUL), future Instruction sets announced by Intel (AVX), as well as future instruction sets proposed by AMD (XOP and FMA4

Hyper Transport Technology rev. 3.1 (3.20 GHz, 6.4 GT/s, 51.6 GB/s, 16-bit uplink/16-bit downlink) [first implemented into HY-D1 revision "Magny-Cours" on the socket G34 Opteron platform in March 2010 and "Lisbon" on the socket C32 Opteron platform in June 2010]

Socket AM3+ (AM3r2)

- 938pin(?), DDR3 support

- will retain only backwards compatiblity with previous Socket AM3/AM2 processors ("new AM3+ socket for consumer versions of Bulldozer CPUs. AM2 and AM3 processors will work in the AM3+ socket, but Bulldozer chips will not work in non-AM3+ motherboards")

Min-Max Power Usage - 10-100 watts

Credits : //en.wikipedia.org/wiki/Bulldozer_(processor)

ปล. เดี่ยวมา Up Bobcat ต่อ คับผม :D